von Nada Tarek

Moderne IC-Designs nutzen zunehmend unkonventionelle Strukturen, was die Extraktion von Widerständen komplexer macht und traditionelle Methoden herausfordert. Neue Frakturierungsansätze wie 1D-, 2D- und fortschrittliche Techniken ermöglichen eine genauere Modellierung parasitärer Widerstände, um Designgenauigkeit, Leistung und Zuverlässigkeit sicherzustellen.

Die Halbleiterindustrie erlebt eine schnelle Entwicklung, die durch die Verbreitung von IoT-Anwendungen, Bildsensoren, Photonik, MEMS-Anwendungen, 3D ICs und anderen neuen Technologien angetrieben wird. Dieses Wachstum hat die Designkomplexität integrierter Schaltkreise (IC) drastisch erhöht. Ein Aspekt dieser Komplexität ist der Einsatz unkonventioneller Strukturen, die nicht dem Manhattan-Layout entsprechen. Dadurch wird eine optimale Funktionalität und Leistung erreicht.

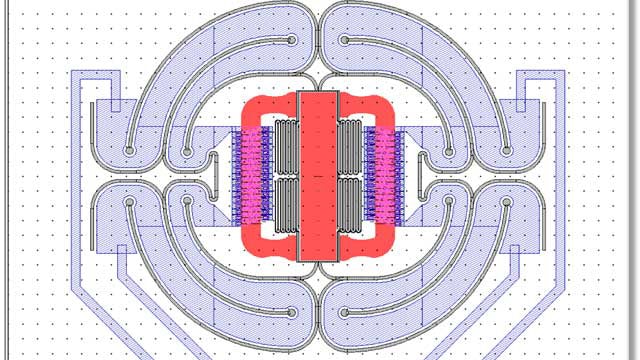

Routing-Beispiele außerhalb des Manhattan-Layouts

3D ICs – Aufgrund des technologischen Fortschritts und der Grenzen des Mooreschen Gesetzes können Entwickler mithilfe von 3D ICs die Architektur in kleinere Chiplets zerlegen. Diese sind in einem einzigen Gehäuse integriert und bieten eine größere Integrationsdichte, höhere Verbindungsgeschwindigkeiten, einen geringeren Stromverbrauch, eine höhere Bandbreite für die Datenübertragung, ein besseres Wärmemanagement und insgesamt geringere Kosten. Ein wesentliches Merkmal des 3D-IC-Designs ist die Verwendung gekrümmter Formen für nicht-Manhattan-Routing-konforme Layouts in Verbindungen und Umverdrahtungen (RDL) zwischen Siliziumdurchkontaktierungen (TSVs) und Mikrobumps. Dies verbessert zwar die Flexibilität und Leistung, bringt jedoch neue Herausforderungen für Entwicklungsaufgaben wie die Widerstandsextraktion mit sich.

Bildsensoren und MEMS-Designs – Bildsensoren, die in Geräten wie Digitalkameras, Smartphones und Überwachungssystemen verwendet werden, fordern eine hohe Bilderkennungsleistung. Um dies zu erreichen, integrieren Entwickler breite Polygone in Layout-Entwürfe. Diese breiten Photodioden-Polygone sammeln mehr Licht, was zu hochauflösenden, rauscharmen Bildern mit hohem Dynamikbereich und niedrigem Stromverbrauch führt. MEMS-Designs nutzen gekrümmte Formen und unkonventionelle Geometrien für eine Vielzahl von Anwendungen in den Bereichen Mechanik, Optik, Magnetik, Fluidtechnik und Biomedizin. Bild 1 zeigt ein Beispiel für ein MEMS-Layout.

Die Verwendung breiter Polygone in Bildsensoren und komplexer Strukturen in MEMS bringen jedoch erhebliche Herausforderungen für die Extraktion des Widerstands mit sich, die ein wichtiger Bestandteil der Zuverlässigkeit des Designs ist. Herkömmliche Feld-Solver sind zwar effektiv, benötigen jedoch oft lange Laufzeiten und sind aufgrund ihrer Rechenkomplexität nicht für die Verifizierung des gesamten Chips geeignet. Entwickler müssen die neueren Frakturierungstechniken nutzen, um die Genauigkeit und Effizienz der Widerstandsextraktion für verschiedene Anwendungen zu verbessern.

Widerstandsextraktion für Entwurfssicherheit

Die Extraktion von Widerständen ist entscheidend für die physikalische Verifizierung des IC-Designs. Eine genaue Widerstandsmodellierung ist für die Vorhersage des Schaltungsverhaltens durch Simulation unerlässlich und gewährleistet die allgemeine Zuverlässigkeit und Genauigkeit der Schaltungsleistung. Mit abnehmender Anzahl der Verbindungen werden die Auswirkungen des parasitären Widerstands immer größer.

Eine präzise Widerstandsextraktion gewährleistet die Zuverlässigkeit, Leistung und Funktionalität von ICs in verschiedenen nachgelagerten Abläufen. Dazu gehören unter anderem die Timing-Analyse, Leistungsanalyse, Elektromigration, Signalintegritätsanalyse, thermische Analyse und Rauschanalyse. Die Timing-Analyse stützt sich beispielsweise auf eine genaue Extraktion des parasitären Widerstands, um Signalverzögerungen abzuschätzen, kritische Pfade zu identifizieren und einen korrekten Timing-Abschluss zu gewährleisten.

Die Extraktion parasitärer Widerstände geht mit erheblichen Herausforderungen einher, z. B. der zunehmenden Komplexität des Designs, der drastischen Verkleinerung der Strukturgrößen und dem Vorhandensein nicht-standardisierter Geometrien, die eine spezielle Handhabung durch fortschrittliche Frakturierungstechniken erfordern.

Verbesserte Frakturierungstechniken für eine präzise Widerstandsextraktion

Für eine präzise Widerstandsextraktion ist es unerlässlich, Geometrien in kleinere Fragmente zu unterteilen, die eine detaillierte Analyse und eine genaue Schätzung der parasitären Widerstände ermöglichen. Bei diesem Verfahren, dem sogenannten Frakturieren, werden komplexe Geometrien in kleinere Teile zerlegt. Der Extraktionsprozess erfasst die Komplexitäten und Details einzelner Komponenten und Verbindungen, was zu einer präziseren Bestimmung von parasitären Widerständen führt. Zu diesen Techniken gehören 1D-Frakturierung, 2D-Frakturierung und weitere fortschrittliche Verfahren, die für den Einsatz bei geschwungenen Formen entwickelt wurden.

1D-Frakturierung:

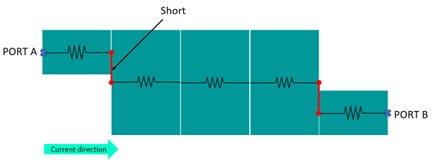

Bei der 1D-Frakturierung wird eine Strecke auf der Grundlage der Stromrichtung in mehrere Bruchstücke in einer Dimension aufgeteilt. Der Widerstand wird für jedes Bruchstück basierend auf seiner Länge, Breite und dem Flächenwiderstand der Schicht berechnet. Während die 1D-Frakturierung bei Standardgeometrien effizient ist, kann es zu Ungenauigkeiten bei Formen mit ungleichmäßigem Stromfluss oder unregelmäßigen Querschnittsprofilen kommen (Bild 2)

Anbieter von EDA-Lösungen sind bestrebt, eine ungleichmäßige Stromverteilung in der 1D-Frakturierung mithilfe komplexer Modelle und Algorithmen in den Griff zu bekommen, um die Widerstandsgenauigkeit auch bei ungleichmäßiger Stromverteilung zu verbessern.

2D-Frakturierung:

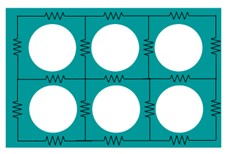

2D-Frakturierung behandelt planare Strukturen und geschlitzte Metallteile, indem Formen in kleinere Polygone zerlegt werden, die die planaren Bereiche abdecken. Dies ermöglicht eine genaue Extraktion parasitärer Widerstände für planare und geschlitzte Strukturen.

Bei geschlitzten Leitern erzeugt das 2D-Frakturieren ein Netz aus Widerständen um die Schlitze und gestattet so eine genauere Widerstandsextraktion als die einfache 1D-Frakturierung (Bild 3).

Fortschrittliche Frakturierung:

Gekrümmte Formen sind entscheidend für Anwendungen wie analoge und HF-Designs, Antennendesigns, MEMS-Bauteile, 3D ICs und Lichtwellenleiter. Fortschrittliche Frakturierungstechniken bewältigen die Komplexität dieser Strukturen effektiver als herkömmliche Methoden.

Fortschrittliche Frakturierungsmethoden, wie das Frakturieren in Richtung des Polygons, zerlegen Strukturen in kleinere Elemente, die sich an den Polygongrenzen orientieren. Diese erlaubt eine präzisere Extraktion des Widerstands. Bild 4 zeigt das Frakturierungspolygon für einen gekrümmten Leiter.

Bewährte Verfahren für Extraktionswerkzeuge der nächsten Generation

Um eine präzise Extraktion des Widerstands zu gewährleisten, sollten Entwickler Design-Automatisierungs-Tools in Betracht ziehen, die neuere Frakturierungstechniken integrieren und auch nicht-Manhattan-Routing-konforme Layouts berücksichtigen.

Eine regelbasierte Extraktionsengine wendet Heuristiken zur Bestimmung der Stromrichtung an und führt dann eine 1D-Frakturierung durch. Anschließend werden Knoten quer zur Stromrichtung erzeugt und der Widerstand zwischen ihnen berechnet. Dies führt zu präzisen P2P-Widerstandswerten für gleichförmige Strukturen, die in den meisten Designs üblich sind.

Um unkonventionelle Strukturen effektiv zu handhaben, sollten Werkzeuge für die parasitäre Extraktion es den Benutzern ermöglichen, die Anwendung von 2D-Frakturierung für eine Leiterbahnschicht unter einer definierten Markerschicht festzulegen. Bei diesem Ansatz wird ein 2D-Netz auf die Leiterbahnschicht aufgebracht, um genaue P2P-Ergebnisse für unkonventionelle Strukturen zu ermöglichen.

Darüber hinaus sollte ein effektiver Ablauf zur Handhabung geschwungener Formen und komplexer Strukturen implementiert werden. Dadurch entfällt die Anwendung eines Feld-Solvers und es werden angemessene Laufzeiten eingehalten. Dieser Ansatz gewährleistet eine präzise Widerstandsextraktion für verschiedene Designszenarien und bietet zuverlässige Leistung und Effizienz bei IC-Designs.

Zusammenfassung

Die genaue Messung des Verbindungswiderstands ist von grundlegender Bedeutung für die Leistungsfähigkeit und Zuverlässigkeit von Schaltungen. Entwickler benötigen fortschrittliche Tools, um geschwungene Formen und komplexe Strukturen zu handhaben und eine schnelle und genaue Punkt-zu-Punkt-Widerstandsextraktion für das gesamte Layout zu ermöglichen.

Autorin

Nada Tarek ist Produktingenieurin in der Calibre Design to Silicon Division bei Siemens EDA. Sie verfügt über mehr als drei Jahre Erfahrung in ihrer derzeitigen Position. Nada Tarek hat sich auf die Unterstützung von PEX- und LVS-Aktivitäten spezialisiert. 2021 schloss sie ihr Studium der Elektronik und Kommunikationstechnik an der Ain Shams University in Kairo, Ägypten, mit einem Bachelor of Science ab. Nada Tarek kam direkt nach ihrem Abschluss zu Siemens, um ihre berufliche Laufbahn in der Industrie zu beginnen.