Die Demonstration eines nichtdestruktiven Lesevorgangs für FeCAPs ist ein Meilenstein auf dem Weg zu Compute-in-Memory-Anwendungen

• Ferroelektrische Kondensatoren (FeCAPs) sind eine energieeffiziente Alternative zu resistiven Speichertypen für analoge Compute-in-Memory (CiM)-Anwendungen.

• Da herkömmliche Lesevorgänge für FeCAPs jedoch destruktiv sind, sind die maximalen Lese-Zyklen durch die Schreib-Zyklen begrenzt, für CiM unzureichend.

• Imec und das Georgia Institute of Technology haben erstmalig einen nichtdestruktiven Lesevorgang gezeigt, der vollkommen entkoppelte Lese- und Schreib-Zyklen ermöglicht.

• Sie erreichten zerstörungsfreie Lese-Zyklen von >1011 und ein kapazitives Speicherfenster von 8,7 (bei 0 V) – die besten Werte, die bisher für FeCAPs berichtet wurden.

Das Versprechen von FeCAPs für Compute-in-Memory

Compute-in-Memory (CiM) hat sich zu einem interessanten Computing-Paradigma entwickelt, um die Speicher- und Stromverbrauchsprobleme in herkömmlichen Designs für Deep Learning-Anwendungen zu meistern. Mit CiM kann ein Teil der für die Ausführung von Deep-Learning-Algorithmen erforderlichen Berechnungen im Speicher selbst durchgeführt werden, wodurch das Verschieben gigantischer Datenmengen zwischen dem Speicher und der Prozessoreinheit vermieden wird.

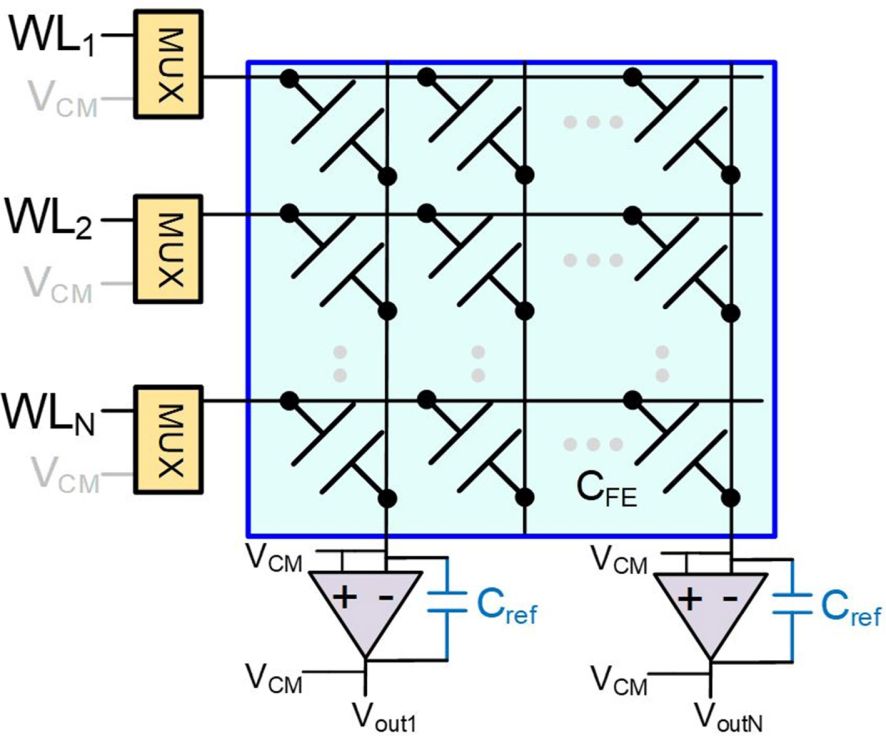

Bei Deep Learning-Algorithmen sind die dominierenden Operationen Matrix-Vektor-Multiplikationen einer Bewertungsmatrix und eines Eingabevektors. Bei diesen Operationen werden die Aktivierungssignale aus dem Eingangsvektor mit vorprogrammierten Wichtungen multipliziert, die in einem Array von Speicherelementen gespeichert sind. Die Ausgabe ist die gewichtete Summe aller Beiträge auf der Summenzeile (oder Bitzeile).

Für die Speicherung der Gewichtungen werden verschiedene Arten nichtflüchtiger Speichertechnologien untersucht. Am beliebtesten sind resistive Speichertypen wie Resistive RAM (RRAM), Phase Change Memory (PCM) und Magnetic RAM (MRAM) – Speicher, die in zwei verschiedenen Widerstandszuständen existieren. Die Speicherelemente sind in Crossbar-Arrays angeordnet und speichern die Gewichtungen als Leitwert.

Vor einigen Jahren begannen Forscher am Georgia Institute of Technology mit der Erforschung der Möglichkeit, ferroelektrische Kondensatoren (FeCAPs) zur Speicherung von Gewichten in analogen CiM-Anwendungen zu verwenden. FeCAPs haben zwei große Vorteile gegenüber resistiven Speichern: (1) die Schaltkreise haben eine deutlich verbesserte Energieeffizienz und (2) es werden keine Selektorvorrichtungen benötigt, da keine Kriechströme durch die Schaltkreise fließen.

Die Notwendigkeit eines nicht-destruktiven Lesevorgangs

Ein FeCAP ähnelt einem herkömmlichen Kondensator, hat aber zwischen zwei Metallschichten (den Elektroden) ein ferroelektrisches Material anstelle einer üblichen dielektrischen Schicht. Ferroelektrische Materialien können in zwei elektrischen Polarisationszuständen existieren – P+ und P- – die durch ein externes elektrisches Feld umgeschaltet werden können. Wird dieses Feld entfernt, behält das ferroelektrische Material seinen Polarisationszustand bei, was der FeCAP ihre nichtflüchtige Eigenschaft verleiht.

Heutzutage ist Hafnium-Zirkonium-Oxid (HZO) aufgrund seines Skalierungspotenzials das ferroelektrische Material der Wahl für Speicheranwendungen. Das herkömmliche Verfahren zum Auslesen des Polarisationszustands von FeCAPs auf HZO-Basis ist jedoch destruktiv: Es beruht auf der Polarisationsumkehr des ferroelektrischen Materials und erfordert daher eine „Neuprogrammierung“ des Polarisationszustands nach jedem Lesevorgang. Folglich ist die maximale Anzahl der Lese-Zyklen an die maximale Anzahl der Schreib-Zyklen gebunden. Die Lese-Zyklen können also nicht unabhängig optimiert werden. Dies ist ein Problem für CiM-Anwendungen, die eine praktisch unbegrenzte Anzahl beim Lesen erfordert, während eine viel weniger Schreib-Zyklen in der Regel ausreichend sind.

FeCAPs mit >1011 nicht-destruktiven Lese-Zyklen und ~8,7 kapazitivem Speicherfenster (bei 0 V)

Auf der IEDM-Konferenz 2023 haben imec und das Georgia Institute of Technology zum ersten Mal eine Lösung vorgestellt, die die Lese- und Schreib-Zyklen von FeCAPs vollständig entkoppeln. Die Lösung basiert auf einer Asymmetrie an den Schnittstellen der beiden Elektroden. Diese asymmetrischen FeCAPs konnten mehr als 1011 Mal ausgelesen werden, ohne den Polarisationszustand des HZO-Ferroelektrikums zu stören. Darüber hinaus wurde ein kapazitives Speicherfenster mit einem rekordverdächtigen Wert von 8,7 bei 0 V Auslesespannung erhalten, was dem Verhältnis zwischen der relativen Permittivität des Ferroelektrikums im P+ und P- Zustand entspricht. Diese Ergebnisse machen FeCAP zu einer vielversprechenden Technologie für CiM-Anwendungen.

Der Mechanismus hinter dem nichtdestruktiven Lesevorgang

Die Fähigkeit, FeCAPs mit einer Lebensdauer von >1011 nichtdestruktiv auszulesen, wurde zum Teil durch die Erforschung der Physik hinter dem Auslesemechanismus erreicht. Ein grundlegendes Verständnis der zugrundeliegenden Prinzipien bietet auch eine solide Grundlage für die weitere Verbesserung der Ergebnisse.

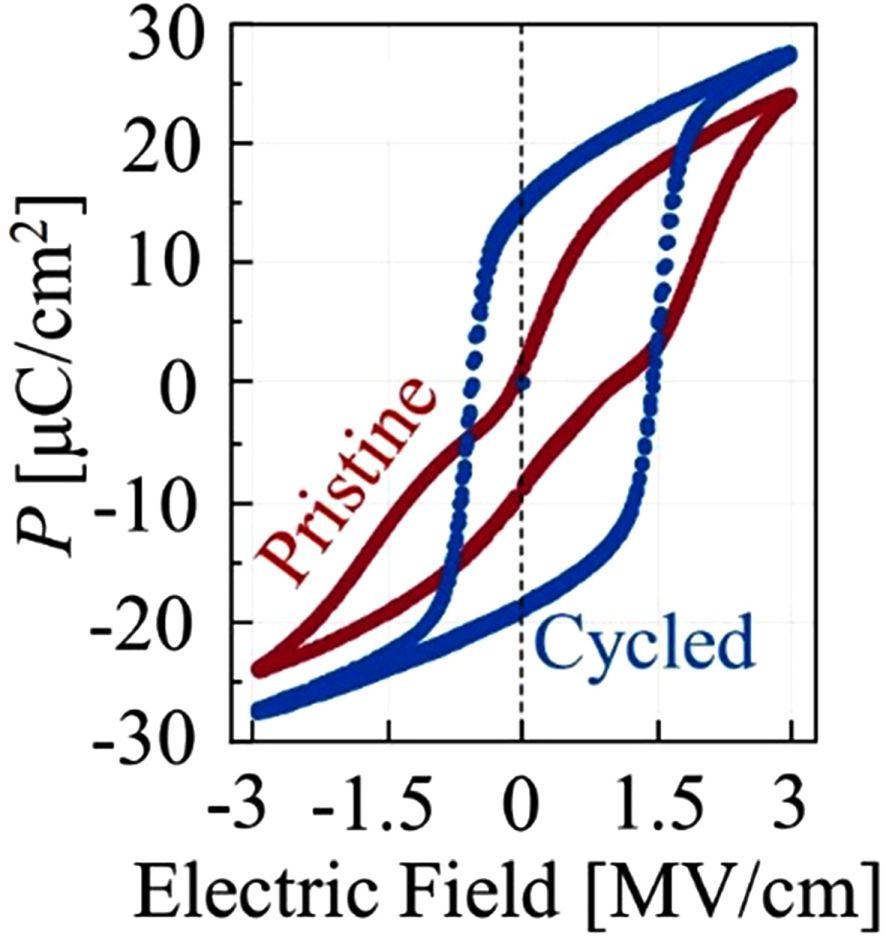

Anders als ein herkömmliches dielektrisches Material weist ein ferroelektrisches Material eine nichtlineare Beziehung zwischen dem angelegten elektrischen Feld und der Polarisationsladung auf, wodurch die ferroelektrische Polarisations-Spannungs-Charakteristik (P-V) die Form einer Hystereseschleife aufweist.

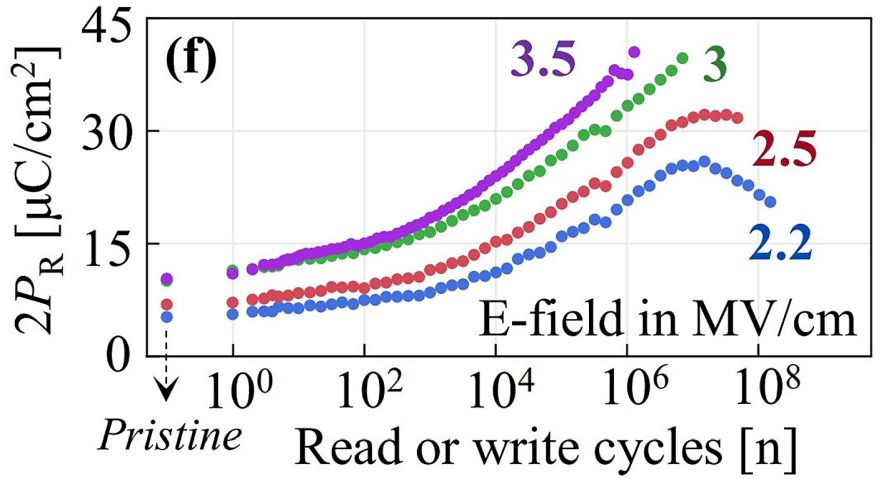

Dieses Phänomen wird bei herkömmlichen Leseverfahren für FeCAPs ausgenutzt. In der Praxis wird ein Spannungsimpuls angelegt, um die Speicherzelle in den anderen Polarisationszustand zu versetzen. Wenn dies geschieht, wird eine Verschiebungsladung, die der Differenz zwischen P+ und P- entspricht, freigesetzt und erkannt. Diese Differenz, die so genannte „Remanente Polarisation“ (2PR), stellt das Speicherfenster dar. Um eine ausreichende Unterscheidung zwischen P+ und P- zu messen, sollte die Restpolarisation 2PR während der gesamten Lebensdauer des Speichers so hoch wie möglich sein. Der größte Nachteil ist jedoch, dass die Zelle nach jedem Auslesen neu programmiert werden muss, wodurch die Leseausdauer von der Schreibausdauer abhängt.

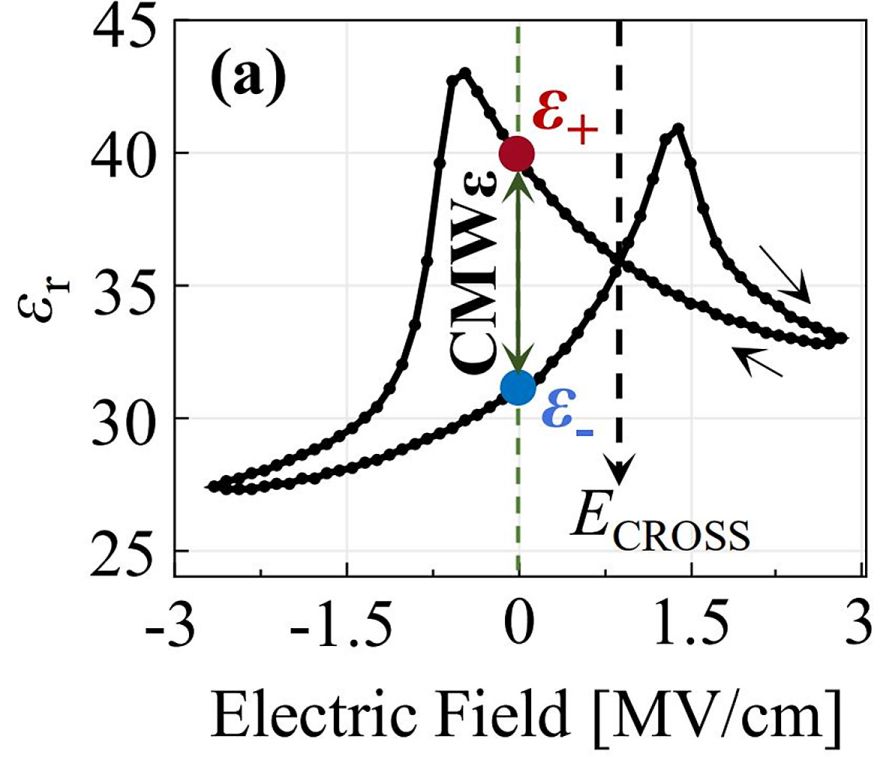

Die Forscher am Georgia Institute of Technology und am imec verfolgen einen anderen Ansatz. Sie gehen von einem anderen Konzept des Speicherfensters aus. Anstatt den Unterschied zwischen P+ und P- auszunutzen, verwenden sie das Konzept eines kapazitiven Speicherfensters. Dieses kapazitive Speicherfenster ist die Differenz zwischen den kapazitiven Zuständen der FeCAP, wenn sie sich entweder im P+ oder im P- Zustand befindet. Es kann aus C-V-Messungen abgeleitet werden, die die nichtlineare kapazitive Reaktion (oder relative Permittivität (eR)) des ferroelektrischen Materials auf ein angelegtes elektrisches Feld aufzeichnen.

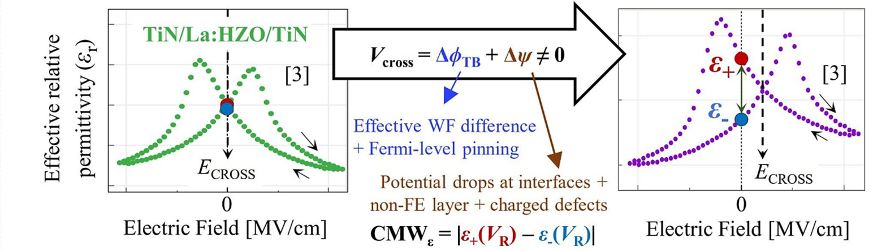

Die C-V-Kurve eines ferroelektrischen Kondensators ähnelt einer symmetrischen Schmetterlingskurve um 0 V, wie im linken Teil von Abbildung 4 dargestellt. Bei 0 V (oder null elektrischem Feld) kreuzen sich die positiven und negativen Zweige der Schmetterlingskurve, was zu einem kapazitiven Speicherfenster von Null führt. Die Forschungsteams haben jedoch einen Weg gefunden, das Speicherfenster bei 0 V zu öffnen, indem sie eine unterschiedliche Arbeitsfunktion für die beiden Elektroden anwenden (siehe den rechten Teil von Abbildung 4). Nach der Optimierung der Grenzflächen zwischen den Elektroden und des Materialstapels konnte ein kapazitives Speicherfenster von ~8,7 bei 0 V erreicht werden.

Die Anwendung quasi-statischer C-V-Messungen zum Auslesen von FeCAPs ist jedoch keine schaltkreisfreundliche Leseoperation. In einem letzten Schritt haben die Forscher gezeigt, dass dieselben Informationen durch Anwendung eines pulsierenden Leseschemas und Auslesen von Ladungen abgerufen werden können, was bei Speicheroperationen üblicher ist. Mit diesem Leseschema erreichten sie >1011 nichtdestruktive Lesezyklen bei einer Vorspannung von 0 V DC, ohne dass das elektrische Feld, bei dem die Polarisation wechselt (d.h. das Koerzitivfeld), angelegt werden muss. Dieses Schema ermöglicht eine vollständige Entkopplung der Lese- von den Schreibzyklen.

Ausblick: Verbesserung der Leistung; Erweiterung des Anwendungsbereichs auf FeRAM; hin zu 3D ferroelektrischen Speichern

Die Forschung wird fortgesetzt, um die Lesezyklen und das kapazitive Speicherfenster von FeCAPs für CiM-Anwendungen weiter zu steigern. Dazu werden der Materialstapel und die Funktionsfähigkeit der Elektroden weiter entwickelt. Das kapazitive Speicherfenster kann auch weiter vergrößert werden, indem der AC-Leseimpuls auf eine von Null abweichende DC-Vorspannung gelegt wird. In diesem Fall muss jedoch darauf geachtet werden, dass das Koerzitivfeld nicht überschritten wird.

Darüber hinaus untersuchen die Forscher am imec die Machbarkeit der Verwendung von FeCAPs und des zerstörungsfreien Ausleseschemas in DRAM-ähnlichen FeRAM-Speicheranwendungen (eingebettet und eigenständig). Es gibt jedoch einige markante Unterschiede zwischen dem klassischen Aktivspeicher und CiM-artigen Operationen. So verlangen Aktivspeicheranwendungen neben hohen Lesezyklen auch wesentlich höhere Schreibzyklen als bei CiM-Operationen. Darüber hinaus werden bei CiM die Beiträge aller Speicherzellen (kleine Signale) auf derselben Bitleitung akkumuliert, bevor das Ergebnis gemessen wird. Bei klassischen Speicheranwendungen muss jedoch der Zustand jeder einzelnen Zelle zuverlässig gemessen werden. Dies stellt strengere Anforderungen an die Größe des Auslesesignals jeder einzelnen FeCAP und erfordert größere Speicherfenster. Das Team erforscht die Spezifikationen für FeRAM-Anwendungen und wie diese erreicht werden können.

Für beide Anwendungen geht der erwartete Trend in Richtung der 3. Dimension, um die Speicherdichte weiter zu erhöhen. FeCAPs werden daher von planaren zu 3D-Kondensatorstrukturen übergehen, was durch den Atomlagen-Abscheidungsprozess für HZO-basierte Kondensatoren ermöglicht wird. Längerfristig könnten FeCAP-basierte Speicher auf peripheren Logikschaltungen integriert werden. Zwei Merkmale der vorgestellten Prozesstechnologie machen dies möglich. Erstens sind, wie bereits erläutert, keine Selektor-Bauelemente (in der Regel ein Transistor) erforderlich, da es keine Kriechströme gibt. Dies ermöglicht die Einbettung der ferroelektrischen Speicher in das Back-End-of-Line (BEOL) der Logikschaltungen. Zweitens liegt das für die Herstellung der HZO-basierten FeCAPs benötigte Wärmebudget – wie z.B. das Niedertemperatur-ALD-Verfahren – unter 400 °C, wodurch die Technologie vollständig BEOL-kompatibel ist.

Fazit

Forscher des imec und des Georgia Institute of Technology haben erstmalig gezeigt, dass es möglich ist, FeCAPs nichtdestruktiv auszulesen und damit die Lese- und Schreibzyklen vollständig zu entkoppeln. Es konnten >1011 nichtdestruktive Lesezyklen nachgewiesen werden, während die Schreibzyklen in etwa bei 107 lagen. Der Auslesemechanismus basiert auf dem Konzept eines kapazitiven Speicherfensters, für das ein rekordverdächtiger Wert von 8,7 nachgewiesen werden konnte. Diese Ergebnisse machen FeCAPs zu vielversprechenden Kandidaten für CiM-Anwendungen. Darüber hinaus legen die Innovationen den Grundstein für die Erforschung des Potenzials von FeCAPs für Embedded- und Standalone-FeRAM-Speicheranwendungen.

Literaturhinweis

Weitere Einzelheiten finden Sie in dem Artikel ‚Pulse-based capacitive memory window with high non-destructive read endurance in fully BEOL compatible ferroelectric capacitors‘, S. Mukherjee et al., IEDM 2023.

Der Autor

Jan Van Houdt wurde an der KU Leuven promoviert. Während seiner Doktorarbeit erfand er den HIMOS Flash-Speicher, den er auf mehrere industrielle Produktionslinien überführte. Im Jahr 1999 übernahm er die Verantwortung für Flash-Speicher bei imec und war damit die treibende Kraft hinter dem Ausbau des Industrial Affiliation Program on Memory Technology von imec. Jan hat mehr als 300 Artikel in internationalen Fachzeitschriften veröffentlicht und über 250 Konferenzbeiträge verfasst ( darunter ~50 Einladungen und fünf Auszeichnungen für den besten Vortrag). Er hat etwa 100 Patente angemeldet und war Mitglied in den Programm- und Organisationskomitees von 10 großen Halbleiterkonferenzen. Im Jahr 2014 wurde er für seine Beiträge zu Flash-Speichergeräten mit dem Titel IEEE Fellow ausgezeichnet. Im selben Jahr startete er das Ferroelektrik-Programm am imec und wurde Gastdozent an der KU Leuven, wo er CMOS- und Speichertechnologie lehrte. Heute ist er Programmdirektor bei imec, imec Fellow und Professor am Fachbereich Physik und Astronomie der KU Leuven.